RISC-V, an open-standard instruction set architecture, has gained traction since its 2010 introduction. Companies like SiFive, Andes, Codasip, Think Silicon, Semidynamics, Synopsys, IBM, Intel, Nvidia, and Qualcomm support RISC-V International through the RISC-V Foundation. SiFive, founded in 2015, leads the pack with over 400 design wins and billions of cores shipped. Its HiFive Premier P550 developer board and Performance P870-D data center solution offer high performance and scalability. RISC-V’s appeal lies in its openness and potential to challenge Arm’s dominance.

The promise of RISC-V as an open-standard instruction set architecture (ISA) introduced in 2010 by David Patterson, Krste Asanovic, and others at the University of California, Berkeley, has been slow to get traction in the industry, but is nonetheless on everyone’s minds and in several companies’s plans.

Several companies such as Andes, Codasip, Semidynamics, SiFive, Think Silicon, and Synopsys, and traditional processor companies like IBM, Intel, Nvidia, and Qualcomm, as well as the popular Raspberry Pi, offer support through the RISC-V International (RVI) in addition to IP libraries. A few companies such as Eswin, StarFive, and XuanTie have released physical processors, and Raspberry Pi offers RISC-V-based single-board computers for education and hobbyists. So the field is quite crowded and very active. Many, if not most, believe RISC-V will supplant Arm’s dominant position in RISC, but it will take decades. Despite some Google-sponsored Android support, mobile is currently out of the question, but for edge applications and automotive, RISC-V is making inroads. In part, this is because the IP competition has pushed prices way below the cost of equivalent IP cores. That low ROI for IP and chip development has taken a toll, pushing Imagination out of the RISC-V space. We expect consolidation in the market too. However, the attractiveness of an open, free ISA is extremely appealing.

In 2015, SiFive was founded by Krste Asanovic (chief architect), Yunsup Lee (CTO), and Andrew Waterman (chief engineer), who created RISC-V at UC Berkeley. The company has raised close to $350 million in investment and is considered the leader of the pack.

Semico Research recently predicted that the RISC-V market will consume over 62 billion cores by 2025 and that RISC-V CPU SIP royalties will reach $230 million by 2028. According to the firm, total SIP licensing revenues were $3.4 billion in 2022.

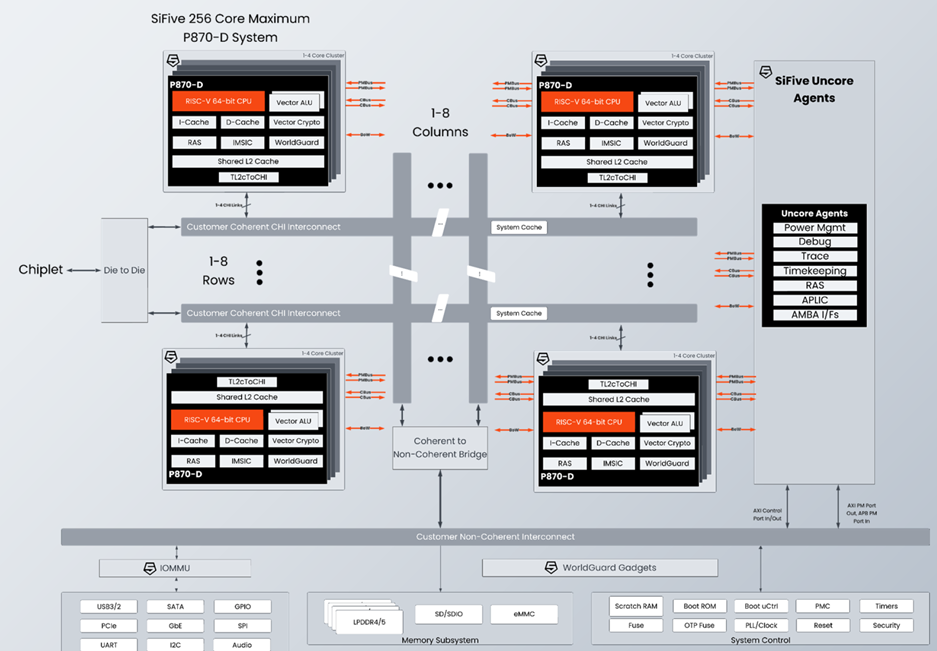

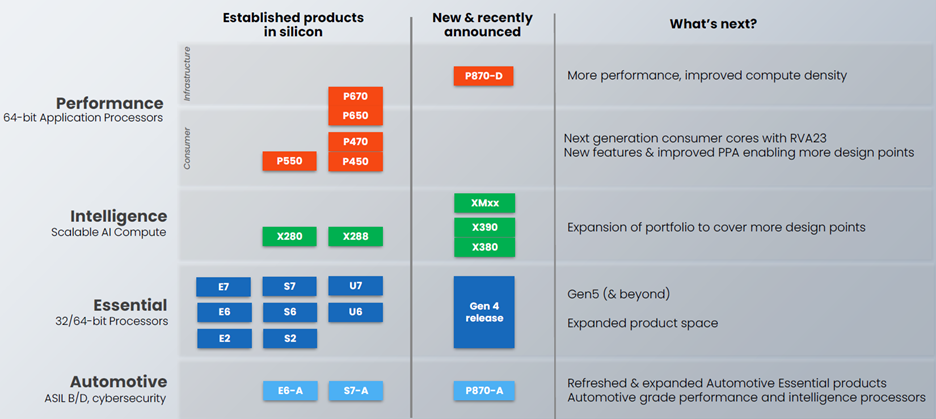

SiFive claims to have over 400 design wins, and its clients are shipping billions of cores to hyperscaler, EV, and IoT markets. The company is now on its fourth-generation of the Essential family. It includes cores from two-stage single issue to eight-stage dual issue, 32- and 64-bit options, improved performance and power efficiency, and the inclusion of industry-standard interfaces. It is offering its HiFive Premier P550 premier board and P870-D data center solution, which it claims is the most performant RISC-V processor available today, emphasizing simplifying and creating scalable systems. The company is also the first IP provider to achieve automotive ISO 21434 certification, while some of SiFive’s IP also has ISO 26262 certification.

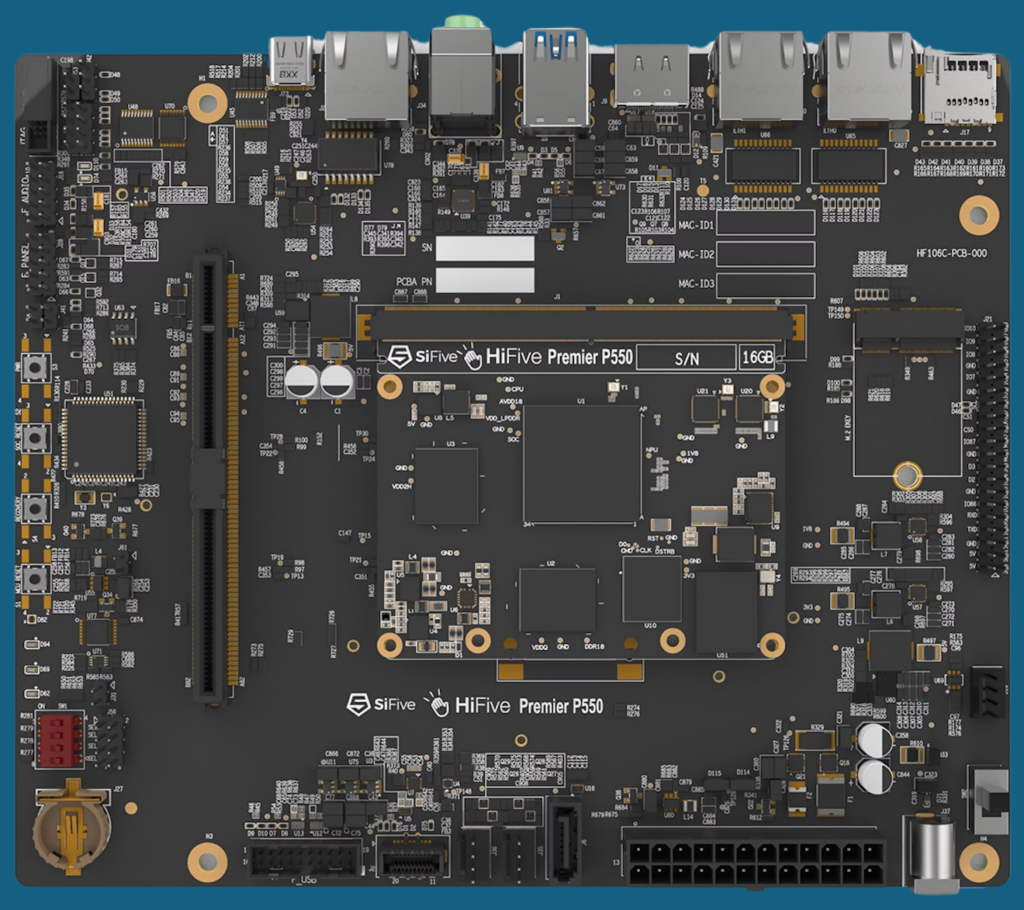

The company has introduced the HiFive Premier P550 dev board to enable software and hardware developers to exploit RISC-V’s potential.

The HiFive Premier P550 is effectively a RISC-V PC, and SiFive expects it to be the fastest-performing RISC-V dev board in the market.

The HiFive Premier P550 board is fabricated in a 12nm process technology; it is a quad-core application processor featuring a 13-stage, triple-issue, out-of-order pipeline with the RISC-V RV64GBC ISA, onboard LPDDR5, eMMC, and PCIe Gen 3. Board features include: 16GB/32GB LPDDR5, 1´ PCIe expansion slot, dual 10/100/1000 Ethernet, SATA 3, 5´ USB 3 ports, onboard GPU, NPU, 2D/3D accelerator, and up to 8K at 50 fps or 28-channel 1080p at 30 fps video encoder/decoder.

In 2021, SiFive introduced the Performance P400 series of RISC-V processor cores, its first efficiency-focused out-of-order processors. The company says its Performance P470 vector application processor, with a 128-bit RISC-V Vector ALU, is capable of 2´ the single-thread performance of an Arm Cortex-A55, achieving greater than 8 SpecINT2k6/GHz, still within similar area and power budgets. That represents a significant upgrade claim to legacy efficiency-class cores currently available.

Its processor range is now from eight-stage, dual-issue, in-order architectures equipped with 256-bit vector engines to advanced three- and four-issue out-of-order processors, with and without vector compute capabilities.

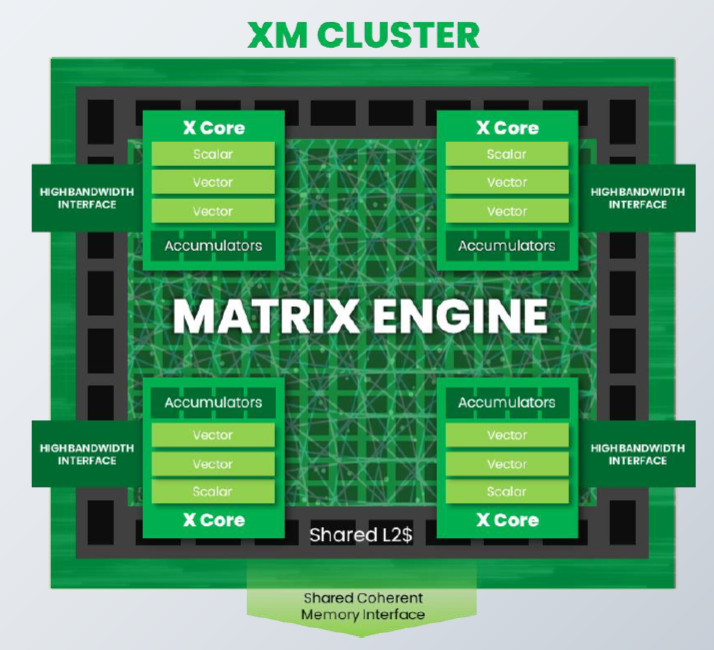

The company has also introduced a matrix engine with fat outer-product design, tightly integrated with four X-Cores, and deep fusion with vector units. It offers four X-Cores per cluster, each with dual vector units. It executes all other layers, for example, activation functions, and has configurable capacity and bandwidth L2 cache. There are new exponential acceleration instructions (up to 64 per cycle per core), and new matrix instructions that are fetched by scalar unit.

Source data comes from vector registers (int8, BF16, FP16, FP32, FP64). The new matrix instructions also provide destination to each matrix accumulator (int32, FP32, FP64).

The XM clusters can connect to memory in two ways: a CHI port for coherent memory access or a high-bandwidth port connected to SRAM or other shared high-bandwidth resources.

What’s next? The company says it will make further investments in software—within SiFive, RISE, and the community—to further optimize software stacks needed by hyperscalers. It will pursue further engagement within RVI around platform standards and continue ongoing CPU investment to drive higher performance.