Ventana has high-performance RISC-V CPUs that can compete with Arm, x86, etc. There is a lot of interest in finding alternatives to Arm, especially in the mobile and automotive space. Arm is obviously not interested in supporting RISC-V with its GPUs, so partnerships with Imagination are critical in the emerging RISC-V client space. There are partners in the mobile and automotive space that are interested in seeing this work.

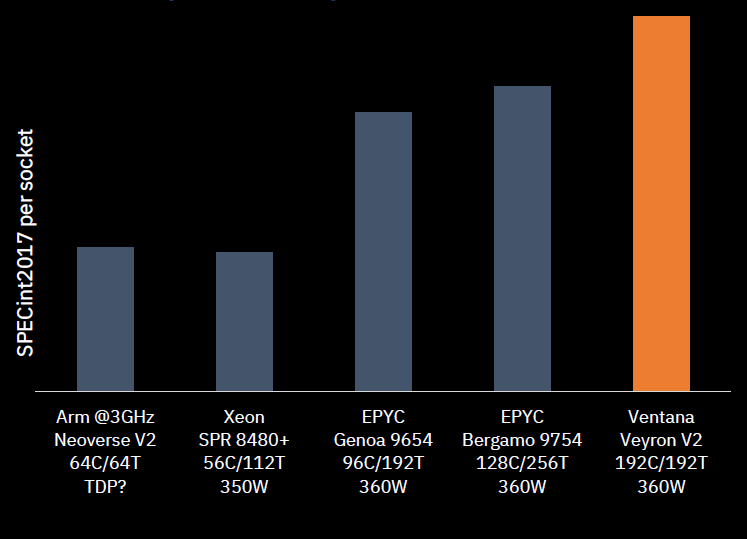

Ventana Micro Systems, founded in San Jose, California, in 2018, plans to build a chiplet processor that can scale from applications—from automotive and edge compute to data center, AI/ML, and hyperscaler—to up to 192 cores using RISC-V architecture. The company plans to offer chips and IP, and its first product is the Veyron V1, introduced at RISC-V Summit in December 2022.

But, a CPU is still, well, just a CPU—RISC, CISC, or otherwise. To make it stand out and a performance leader, you need a SIMD parallel processor accelerator—some people call them GPUs. They can do graphics, but the G stands for giga-everything.

To build such a heterogeneous SoC, Ventana turned to one of the most experienced GPU IP companies, Imagination Technologies. Both companies are premier members of RISC-V International and the RISC-V Software Ecosystem (RISE) project and are strong advocates of open architecture.

Though there are over 3,000 member companies involved with the software ecosystem development, this partnership between Ventana and Imagination is an important step forward for the industry, as it brings together two processor developers in their respective fields. With their combined expertise in CPUs and GPUs, the two companies are well positioned to bring a new configuration to the RISC-V open architecture.

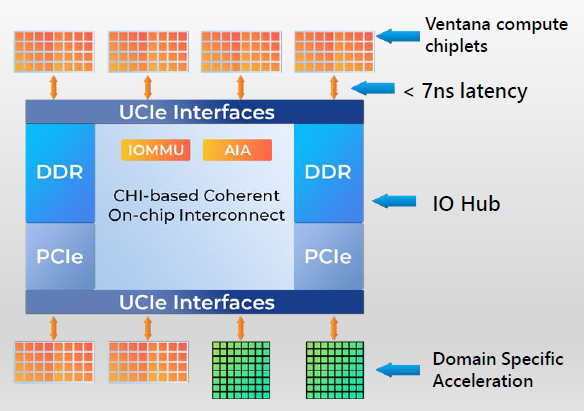

The two companies will be showing an emulation model of an Imagination GPU working with a Ventana RISC-V CPU at the RISC-V Summit next week. Ventana is about to launch the Veyron V2 next week, so this launch is aligned around that. The key change with V2 is that the RISC-V ISA now has most of the necessary features to compete with x86/Arm such as a standard vector extension and IOMMU specification. It will include:

- Hypervisor extension

- Type 1 and 2 Hypervisors; nested virtualization

- Advanced Interrupt Architecture (AIA)

- Including native MSI handling and interrupt virtualization

- External and self-host debug; trace-to-memory

- Rich set of performance events and perf counters

RVA23 feature set includes UCIe chiplet interface, +40% performance, 512b vector unit + AI matrix extensions, server-class IOMMU and platform for RISE software compatibility, and domain-specific acceleration (DSA).